# FIMCE: A Fully Isolated Micro Computing Environment For Multicore Systems\*

SIQI ZHAO, Singapore Management University, Singapore XUHUA DING, Singapore Management University, Singapore

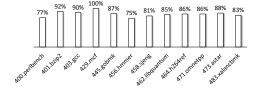

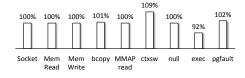

Virtualization-based memory isolation has been widely used as a security primitive in various security systems to counter kernel-level attacks. In this paper, our in-depth analysis on this primitive shows that its security is significantly undermined in the multicore setting when other hardware resources for computing are not enclosed in the isolation boundary. We thus propose to construct a fully isolated micro-computing environment (FIMCE) as a new primitive. By virtue of its architectural niche, FIMCE not only offers stronger security assurance than its predecessor, but also features a flexible and composable environment with support for peripheral device isolation, thus greatly expanding the scope of applications. In addition, FIMCE can be integrated with recent technologies such as Intel Software Guard Extensions (SGX) to attain even stronger security guarantees. We have built a prototype of FIMCE with a bare-metal hypervisor. To show the benefits of using FIMCE as a building block, we have also implemented four applications which are difficult to construct by using the existing memory isolation method. Experiments with these applications demonstrate that FIMCE imposes less than 1% overhead on single-threaded applications, while the maximum performance loss on multithreaded applications is bounded by the degree of parallelism at the processor level.

CCS Concepts: • Security and privacy → Virtualization and security;

Additional Key Words and Phrases: Virtualization, Isolation, Multicore Platform, Hypervisor

#### **ACM Reference Format:**

#### 1 INTRODUCTION

Hardware assisted virtualization has become one of the mainstream features of modern commodity processors in high-performance servers, personal computers, and even mobile phones. With hardware virtualization support, a hypervisor running directly on the hardware is more privileged than operating systems (OSes). The literature on virtualization-based security has shown that compact bare-metal hypervisors can be used to to harden the kernel [28] and to cope with the kernel-level attacks on applications [6, 9, 10, 16, 18, 24, 38] and I/O channels [8, 29, 42]. The security primitive commonly used in these systems is virtualization based memory isolation via a special paging

Authors' addresses: Siqi Zhao, School of Information Systems, Singapore Management University, Singapore; Xuhua Ding, School of Information Systems, Singapore Management University, Singapore.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2017 Association for Computing Machinery.

2471-2566/2017/1-ART1 \$15.00

https://doi.org/10.1145/nnnnnnnnnnnnn

<sup>\*</sup>The conference version of this work [40] focuses more on uncovering security pitfalls of virtualization-based memory isolation and sketches out FIMCE as a solution. This manuscript elaborates the system design details of FIMCE (Section 5.2) and compares it with other virtualization-based isolation (Section 5.3). Other major additions include a discussion on SGX and FIMCE (Section 6), a detailed description of FIMCE's modularized software infrastructure (Section 7), and more implementation details (Section 9.2).

structure introduced by Memory Management Unit (MMU) virtualization. For example, Intel's virtualization technology uses the so-called Extended Page Tables<sup>1</sup> (EPTs) which are traversed by the hardware during address translation. The EPTs (and their counterparts on non-Intel processors) are solely managed by the hypervisor and are not accessible to any guest software including the kernel. Thus, by setting the access permission bits on the EPTs, the hypervisor is empowered to police memory accesses in the guest so that sensitive memory pages can be isolated from the untrusted software.

Most existing systems [9, 18, 24, 28] built on memory isolation implicitly assume a unicore platform. Although the eXtensible and Modular Hypervisor Framework (XMHF) [35] and the On-demand Software Protection (OSP) [10] explicitly describe their mechanisms in a multicore setting, their designs essentially impose a single-threaded execution model for the hypervisor. Nonetheless, the prevalence of multicore processors in a wide spectrum of computing devices (from mobile phones to high-performance servers) necessitates revisiting the memory isolation primitive in the multicore context. We observe that parallel execution on a multicore platform makes a subtle, yet far-reaching impact on security, because the adversarial thread on one core can attack the protected thread on another, a scenario that never occurs on a unicore system.

Our work presented in this paper begins with an in-depth analysis of memory isolation in a multicore setting. After scrutinizing both the hardware architecture and the system design, we identify several security and performance complications, including cumbersome EPT management, insecure page table verification and incapable thread identification. To validate our assertion that the memory isolation primitive is *ineffective*, we have schemed and implemented two attacks on XMHF [35] and BitVisor [29], respectively, to successfully invade protected memory pages.

The deep-seated reason of ineffective isolation is that the current isolation schemes ignore other critical elements in a computing environment including, most notably, the Central Processing Unit (CPU) core. The incomplete isolation boundary thus becomes an exploitable vulnerability in a multicore setting as it allows for parallel executions. We hence propose the *Fully Isolated Micro Computing Environment* (FIMCE) as a new isolation primitive for multicore platforms. FIMCE integrates memory isolation with core isolation and optionally I/O device isolation. It offers stronger security than the existing primitive with a much reduced attack surface, and is also more versatile to support more types of applications.

FIMCE features a malleable hardware setting which can serve different security needs. Its software infrastructure in the isolated environment is constructed in a modular fashion according to the application demands. Thus it does not require the protected application code to be self-contained. Due to its architectural niche, it can also be used as a trusted environment running in parallel with the untrusted kernel in order to monitor kernel activities. We have implemented a prototype of FIMCE including a micro-hypervisor. We have also measured its performance by running benchmarks and built four security systems to showcase its versatility. The experimental results confirm FIMCE's strong security and high usability, with a modest cost of performance due to a less degree of parallelism available for the OS to use.

Recent years have witnessed the booming adoption of Intel's Software Guard Extensions (SGX) technology to isolate the memory and execution of security-sensitive code. With the hardware enforcing memory access policies, SGX-based isolation attains stronger security than hypervisor-based isolation. Nonetheless, SGX lacks the capability of I/O device isolation and requires the (untrusted) OS to set up and configure enclaves. In contrast, FIMCE offers built-in I/O support and has no dependence on the OS. In this paper, we also compare FIMCE and SGX in detail and show how the two techniques can be integrated to complement each other.

<sup>&</sup>lt;sup>1</sup>The equivalent structure is called the Nested Page Table on AMD's processors and the Stage 2 page table on ARM processors.

The main contributions of our work are summarized below.

- (1) We show that the existing virtualization-based memory isolation primitive is ineffective on multicore platforms. Our assessment is based on an in-depth examination upon design defects and is evidenced by concrete attacks on XMHF [35] and BitVisor [29].

- (2) We propose FIMCE as a new isolation primitive for multicore systems. It offers stronger security and better versatility than its predecessor. The key idea behind FIMCE is to isolate all hardware resources needed by the protected execution, instead of memory pages only.

- (3) We implement a prototype of FIMCE and assess its performance with benchmarks. We also use it as a building block to construct several security applications in order to showcase its attractive features including the modularized software infrastructure, I/O support, and the malleable hardware setting.

Organization. In the next section, we explain the background of address translation and memory accesses in multicore systems. Then, we show two concrete attacks on XMHF and BitVisor in Section 3, followed by an in-depth examination of memory isolation in Section 4. We propose the design of FIMCE in Section 5 and compare it with SGX in Section 6. Next, we present the software architecture of FIMCE in Section 7, and discuss possible applications of FIMCE in Section 8. Section 9 evaluates security and performance based on experiments with a FIMCE prototype. We describe the related work in Section 10 and conclude the paper with Section 11.

## 2 BACKGROUND

Address Translation with Virtualization. With hardware-assisted memory virtualization, address translation proceeds with two stages for any memory access from the guest. In the first stage, the MMU translates a virtual address (VA) into a Guest Physical Address (GPA) by walking the guest page tables managed by the kernel. In the second stage, the MMU translates a GPA to a Host Physical Address (HPA) by traversing the EPTs managed by the hypervisor. The roots of the guest page tables and the EPTs are stored in the CR3 register and a control structure field called EPT Pointer, respectively. During address translation, the MMU aborts if the memory access conflicts with the permissions specified in these page tables.

To reduce the latency of address translation, Translation Lookaside Buffers (TLBs) are used by each CPU core to cache those recently used translations and access permissions. The MMU traverses the paging tables only when the TLBs do not store the matching entry. However, unlike data and instruction caches, it is the software, instead of the hardware, that maintains consistency between the TLBs and the paging tables. The operating system and the hypervisor are expected to invalidate the relevant TLB entries after updating the page tables.

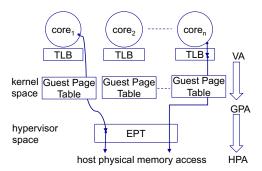

Memory Access in Symmetric Multiprocessor (SMP) Systems. In an SMP setting, multiple cores access the shared physical memory as shown in Figure 1. Nonetheless, they may use different address mappings since address translation is performed independently by each core's MMU. The VA-to-GPA mappings on all cores are controlled by the guest kernel. Depending on the running threads, the cores may or may not use the same set page tables. The GPA-to-HPA mappings are controlled by the hypervisor. By default, *all* cores use the same set of EPTs since the GPA-to-HPA mappings are for the entire virtual machine and the guest kernel's thread scheduling is transparent to the hypervisor.

In the SMP setting, it is more complicated to maintain TLB consistency since the threads in each core may modify the shared page tables while the TLBs are local to each core. Typically, the thread that modifies the paging structures performs the so-called TLB shootdown whereby the thread on the initiating core fires an Interprocessor Interrupt (IPI) to other cores. Upon the arrival of an

Fig. 1. The paradigm of memory access in an SMP setting. The first core has TLB misses and accesses the memory via the guest page tables and the EPTs, while the last core has TLB hits and accesses the memory without consulting any page table.

IPI, a handler is invoked to invalidate those stale TLB entries on the affiliated core. The Advanced Programmable Interrupt Controller (APIC) is responsible for receiving and sending IPIs. Its proper behavior affects the success of TLB shootdown and consequently TLB consistency.

#### 3 ATTACKS

As a prologue to our in-depth analysis of memory isolation and the proposal of FIMCE, we present concrete attacks on two open-source micro-hypervisors, BitVisor [29] and XMHF [35], running on a desktop computer with multiple cores. The intention is to exemplify the weakness of the widely used memory isolation primitive, instead of targeting at these two systems alone. The success of the attacks indicates that it requires meticulous checking of all system design details to realize memory isolation in multicore settings.

Without loss of generality, consider a typical isolation scenario where the hypervisor receives the request from a security sensitive application at runtime, and then sets the read-only permission in the EPT entry for the application's code page. The objective of our attacks is for the malicious OS to successfully modify the protected page without the write permission on the EPT entry. The general idea behind the attacks is to use a stale TLB entry so that the core continue to use the write permission granted before the EPT update. Next, we describe the stifling attack and the Virtual Processor ID (VPID) attack.

# 3.1 Stifling Attack

The *stifling attack* prevents the CPU core controlled by the malicious thread from responding to the hypervisor's TLB shootdown, so that its stale TLB entry is not invalidated. Note that trapping to the hypervisor cannot be denied by setting the interrupt masking bit (namely EFLAGS.IF), because the hardware ignores it whenever the External-interrupt Exiting bit in the Virtual Machine Control Structure (VMCS) is set.

Our attack exploits a hardware design feature to block all maskable external interrupts, including the IPI used for TLB shootdown. According to the hardware specification, the IPI handler is expected to perform a write to the End Of Interrupt (EOI) register in the local APIC before executing an iret instruction. The EOI write operation signals the end of the current interrupt handling and allows the local APIC to deliver the next IPI message (if any) to the core. If no such write is performed, the local APIC withholds subsequent IPIs and never delivers them.

4

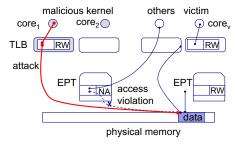

We explain the attack details with an example. As depicted in Figure 2, suppose that the victim application occupies  $core_v$  while two malicious kernel threads occupy  $core_1$  and  $core_2$ . The attack steps are described below.

- (1) At core<sub>v</sub>: The victim application starts to run and writes data into a memory buffer.

- (2) At core<sub>1</sub>: The malicious kernel maps the guest physical address of the buffer into its own address space by changing its guest page table. It reads the buffer so that the corresponding EPT entry is loaded in the TLB of core<sub>1</sub>. It also disables interrupt and preemption so that it is not scheduled off from core<sub>1</sub> in order to avoid any TLB invalidation due to events within the guest.

- (3) At core<sub>2</sub>: Another thread of the malicious kernel sends an IPI to core<sub>1</sub> by using a legitimate IPI vector for OS synchronization.

- (4) At core<sub>1</sub>: The malicious IPI handler returns without writing to the EOI register of the local APIC. As a result, subsequent IPIs are never accepted by core<sub>1</sub>.

- (5) At core<sub>v</sub>: The victim issues a hypercall for memory protection. The hypervisor updates the EPT for all other cores to disallow accesses. It broadcasts an IPI to trigger VM exit on other cores.

- (6) At core<sub>1</sub>: The IPI from core<sub>v</sub> is not delivered to core<sub>1</sub>. The kernel thread can continue to read/write the isolated data buffer without trigger any EPT violation, because the core's MMU uses the EPT entry in the TLB which has the stale permissions assigned prior to the hypercall.

Fig. 2. Illustration of the stifling attack bypassing the EPT's access control over the victim's data. The attacker controls core<sub>1</sub> and core<sub>2</sub>.

We have implemented the attack on BitVisor [29] with necessary changes including new code to change EPT permission bits for isolation and an interrupt handler for TLB shootdown. The experiment shows that the kernel successfully writes to the protected buffer, even though the access permission in the corresponding EPT entry has been changed into read-only.

One possible countermeasure to the stifling attack is to virtualize local APICs so that the hypervisor intercepts the external interrupts and enforces EOI writes. However, this approach not only increases the hypervisor's code size and complexity, but also has performance tolls as it is recommended to remove the hypervisor from the code path handling interrupts for better efficiency [17, 33].

## 3.2 Virtual Processor ID (VPID) Attack

XMHF [35] is an open-source micro-hypervisor on x86 platforms that explicitly takes the multicore setting into its design consideration. To deal with concurrency in the hypervisor space, XMHF enforces a *single threaded* execution model for the hypervisor. When one core is trapped to the hypervisor space, it "quiesces all other cores" by broadcasting an Non-maskable Interrupt (NMI)

which triggers a VM exit and effectively pauses the execution of all other threads across the system. Therefore, it is not subject to the stifling attack. Nevertheless, it still has another TLB-related vulnerability.

Recent generations of x86 processors introduce a feature called Virtual Processor ID (VPID) to avoid unnecessary TLB invalidation induced by VM exit events. Identifiers are assigned to address spaces of each virtual CPU and of the hypervisor and attached to their TLB entries. When a TLB entry is hit during translation, it is valid only when its VPID tag matches the VPID of the present address space. With this extra checking, the hardware does not need to invalidate *all* TLB entries during VM exit.

Although improving the performance, this technology has an unexpected security side-effect. Since not all TLB entries are evicted by the hardware during a VM exit, the stale entries of the guest must be explicitly invalidated by the hypervisor. However, the XMHF hypervisor neglects this issue. It assigns VPID 0 to the hypervisor and VPID 1 to the guest. Unfortunately, there is no explicit invalidation of TLB entries tagged with VPID 1 when handling the quiesce-NMI. With this loophole, we devise the following attack for the guest OS to write the page set as read-only by the EPTs. The system setting is the same as the stifling attack shown in Figure 2.

- (1) At core<sub>v</sub>: The victim application starts execution. It allocates a page and requests memory isolation.

- (2) At core<sub>1</sub>: The malicious kernel running on core<sub>1</sub> maps the buffer into its own space, reads it once so that a TLB entry is loaded by the MMU. It disables interrupt and preemption so that the TLB entry is not evicted by events in the guest.

- (3) At core<sub>v</sub>: The victim application performs a hypercall to the XMHF hypervisor. The hypervisor issues an NMI to trap other cores and sets the read-only permission bit in the relevant EPT entry after CPU quiesce.

- (4) At core<sub>v</sub>: The execution returns to the victim application.

- (5) At core<sub>1</sub>: The guest OS resumes its execution. Due to incomplete TLB invalidation, the stale entry is not removed. The guest OS continues to read and write the page, regardless of the permission in the current EPT.

The implementation involves a hypervisor application, or hypapp in XMHF's terminology, based on XMHF Application Programming Interfaces (APIs). The hypapp takes an address of a physical page as input and sets its access permission in EPTs as read-only. The hypapp is invoked via a hypercall from an application bound to a core. The kernel runs a malicious thread on another core to continuously access the page. We observed that the malicious thread keeps a stale TLB entry and successfully writes the target page without triggering EPT violation.

**Caveat.** We reiterate that the intention of presenting the attacks above is not to show the vulnerability of these schemes, but to emphasize that applying memory isolation in the multicore setting is *not* as straightforward as it seems. The low-level system subtleties, if not treated properly and thoroughly, weaken the security strength. The next section provides more insights into this issue.

## 4 IN-DEPTH EXAMINATION OF MEMORY ISOLATION

Memory isolation is the primitive used in almost all virtualization based security systems [9, 13, 18, 24, 28, 32, 35]. It denies any unauthorized access to the concerned physical memory pages. Most existing schemes in the literature focus on how to make use of it to achieve their high-level security goals, assuming that the primitive itself is secure. In this section, we examine its security under the multicore context.

# 4.1 System and Threat Models

The system in consideration is a commodity multicore platform running a bare-metal microhypervisor with a single guest virtual machine. The adversary is the guest kernel which is subverted and controlled by malware. With kernel privilege, the adversary can launch arbitrary software-based attacks, such as illicit memory accesses and execution context manipulation. It may even use a CPU emulator to emulate the hypervisor's behavior. We assume that the Basic Input / Output System (BIOS), the firmware and the hardware in the platform are not compromised by the adversary and behave in compliance with the respective specifications. We trust the micro-hypervisor code, data and control flow throughout the lifetime of the platform. We do not consider side channel attacks nor denial-of-service attacks. For the convenience of presentation, we use "the guest" and "the kernel" throughout the paper to refer to the virtual machine in the system and its kernel, respectively. Note that the models described above mirrors those used in the literature [9, 13, 18, 24, 28, 32, 35].

## 4.2 The Common Practice of Memory Isolation

Early memory isolation schemes (e.g., Overshadow [6]) use para-virtualization with the shadow page tables so that the hypervisor effectively manages all address mappings. With the advent of CPU and MMU virtualization, most recent systems rely on the access control feature provided by the EPTs. These schemes do not explicitly declare whether they run on the multicore setting or not, except XMHF [35]. We consider a generic procedure in the unicore setting to explain the common practice of memory isolation widely used in the literature, including SecVisor [28], TrustVisor [24], SPIDER [13], InkTag [18], AppShield [9], and Heisenbyte [32]. The primitive consists of the following steps.

- **Step 1.** The hypervisor is instructed to isolate a data page at the virtual address  $VA_{data}$  (e.g., via a hypercall) so that  $VA_{data}$  can be accessed by the authorized code with permission p and by any unauthorized code with permission  $\hat{p}$ . For instance, p can be read and write while  $\hat{p}$  can be read-only so that unauthorized code cannot modify the page.

- **Step 2.** The hypervisor traverses the present kernel page table to obtain the corresponding guest physical address  $GPA_{data}$  and then traverses the EPT to locate the entry  $\delta$  that maps  $GPA_{data}$  to the host physical page  $HPA_{data}$ . It sets the permission bits on  $\delta$  according to  $\hat{p}$ .

- Step 3. At runtime, if the hypervisor determines that the requested access is from the authorized code, it sets the permission bits on  $\delta$  according to p. When the hypervisor detects that the authorized code execution is to be scheduled off from the CPU (e.g., due to interrupts), it flushes the TLBs and restores permission  $\hat{p}$  on  $\delta$ .

A variant of the above method is to switch the mapped physical address inside  $\delta$  so that different views of physical memory are presented depending on the trustworthiness of the running thread on the core. SPIDER [13] and Heisenbyte [32] are exemplary systems using this approach.

# 4.3 Complications of Memory Isolation In Multicore Setting

The aforementioned memory isolation procedure runs securely on a unicore platform. However, its vulnerability is exposed in the multicore setting due to parallel execution. A malicious thread on one core can attack the trusted thread on another core. In the following, we present an in-depth analysis of the complications from three perspectives.

4.3.1 Cumbersome EPT Management. As shown in Section 2, each CPU core makes independent accesses to the physical memory. Therefore, the access permission p for the trusted code and the permission  $\hat{p}$  for the untrusted code may co-exist in the system, which has two implications. Firstly, it is no longer sufficient to maintain a single set of EPTs which gives all cores the same access

rights. At least two sets of EPTs are needed, with one for the trusted execution and the other for the untrusted. In general, consider a system with n CPU cores and k applications requesting for memory isolation. The hypervisor has to maintain k+1 different versions of permission settings. In the worst runtime scenario, the hypervisor has to properly install n distinct EPTs simultaneously. A more complicating issue is that the hypervisor should have an algorithm to detect potential conflicts and/or inconsistency among the permission policies. The workload of managing multiple EPTs not only expands the hypervisor code size, but also significantly complicates its logic.

The second issue is about the switch from the high-privilege permission (e.g., read and write) to the low-privilege permission (e.g., non-accessible). Privilege downgrade mandates that *all* relevant EPT entries and TLB entries be updated consistently. Our attacks in Section 3 have shown that it requires a deep understanding of the low-level hardware behavior and sophisticated programing skills to make the switch.

4.3.2 Insecure Guest Page Table Checking. In the common practice described in Section 4.2, the trusted threads and untrusted threads use distinct EPT settings. However, they may use the same guest page tables managed by the guest kernel. Checkoway et al. have proposed the Iago attack [5] to show that the malicious kernel can manipulate the VA-to-GPA mapping to attack memory isolation. On a unicore system, the hypervisor can arguably verify such data structures before entering the isolated environment. After being verified, they are not subject to malicious modification since the guest OS is not running at the same time. Following this approach, InkTag [18], TrustVisor [24] and AppShield [9] have implemented kernel page table verification/protection when the hypervisor sets up the isolation environment and while the protected thread is in execution.

However, this approach is not secure due to the race condition attacks in the multicore setting. Note that the verification of the guest page table cannot be instantly completed. The hypervisor has to walk through the entire guest page table and set the permission bits in the EPT. InkTag, TrustVisor and AppShield do not enforce core quiesce. The guest kernel and the hypervisor can execute simultaneously. Therefore, the race condition attack can cause the access control policy to be mistakenly enforced on unintended pages while the target pages remain unprotected.

We use the following example to illustrate this. Suppose that a security-sensitive program is just launched and the hypervisor needs to setup its isolated environment. In order to lock and verify the current guest page tables, the hypervisor has to find where they reside. In other words, it has to locate all physical memory pages occupied by the guest page tables, so that it is able to configure the corresponding EPT to lock them. Unfortunately, the hypervisor does not have the prior knowledge, because the guest page table is priorly managed by the kernel. Therefore, the hypervisor has to traverse all guest page table entries starting from the root pointed to by the CR3 register in order to find out their physical locations. Page table traversal by software is a lengthy operation because it involves a great amount of mapping and memory access operations. Thus, the guest OS running on another core has a non-negligible time window to change one of the leaf page tables after it is verified but before it is locked. If the traversal is along the ascending order of the address space, the page table pages for the lower end addresses are easier to attack because they are exposed for a longer time interval. In our experiment, it takes around 120,000 CPU cycles to lock the entire page table used by a simple application, which is long enough for the kernel to tamper with one page table entry. As a result, the guest page table locked up by the hypervisor is not the actual one used by the security-sensitive program, which makes it vulnerable to the Iago-like attack.

Note that the core quiesce technique used in XMHF can defeat the aforementioned race-condition attack, since it stalls all untrusted execution. However, it incurs a remarkably high performance cost. The hypervisor needs to find out all physical pages for the guest page table, sets the corresponding

EPT entry to prevent the kernel's modification, and verifies whether the guest page table harbors any poisonous mappings. All guest threads are paused during the hypervisor's processing.

4.3.3 Incapable Thread Identification. Since the trusted threads and the untrusted threads run in parallel, the hypervisor has to differentiate them and apply the appropriate EPTs for the respective execution. Therefore, a prerequisite of secure isolation is to correctly identify the subject that intends to access the protected memory pages.

The subject identity of the security-sensitive program piggybacks on a kernel-level abstraction, e.g., process or thread. A high-level access policy is in the form of "Process X is allowed to read and write page #n; and other processes cannot access". To enforce such a policy in the EPT, the hypervisor maintains the association between the process X and the protected physical pages. Typically, it is implemented by using the present the CR3 register content (e.g., as in TrustVisor [24]) or the combination of CR3 and the address of the kernel stack (e.g., as in AppShield [9]).

It is a challenging task for the hypervisor to correctly identify the subject requesting memory access. The hypervisor sits underneath the OS and lacks the semantic knowledge of the execution. It is only able to acquire the hardware-related information, such as the instruction pointer stored in the EIP register and the page table root address stored in the CR3 register. Note that interpretation of their application semantics involves kernel objects. For instance, the EIP register stores the virtual address of the next instruction to execute. It requires the guest page table managed by the kernel to derive its guest physical address. Since the kernel is untrusted, it is not straightforward for the hypervisor to *correctly* infer the logical representation of the subject from the hardware information.

Overshadow [6] uses the hypervisor-supplied Address Space ID (ASID) and its associated thread context's address to identify the subject. Nonetheless, the guest page table is also involved in storing and retrieving the ASID. Therefore, its security remains as weak. In the following, we consider a security-sensitive program P whose data buffer has been isolated by the hypervisor and show the impersonation attacks upon CR3 and ASID based identification.

**Impersonation Attack.** Suppose that the CR3 register is used to identify the subject. The malicious guest OS can schedule off P and launch a malicious process P' with the same CR3 content as P's, but with different contents in the page table root page. When P' issues a hypercall, the hypervisor mistakenly believes that the subject is P. As a result, P' may exfiltrate the secret of P and tamper with its data. Enclosing kernel-related objects such as the stack address is not secure either because they are still subject to forgery. Suppose that a hypervisor-supplied object such as the ASID is used to identify the subject. Program P needs to store its ASID and to explicitly supply it to the hypervisor in order to access its isolated memory. Nonetheless, this method ends up with the chicken-and-egg dilemma. On one hand, if P's ASID is unprotected, it can be used by P' with the kernel's assistance. On the other hand, if the ASID is restricted to be used by P only, the hypervisor does not have the clue to decide when the ASID is used by P or P' which is also an identification problem.

To summarize, the memory isolation primitive in the multiple core setting is more complicated than it appears. Setting the permission bits on the EPT does not suffice to attain the desired security. The complications are mainly caused by two factors. The first factor is the design defect of the current memory isolation technique used in the literature. The boundary between the trusted and the untrusted is only drawn upon the GPA-to-HPA mapping. The VA-to-GPA mappings and the CPU core are still controlled by the adversary, which exposes a large attack surface. The second factor is execution parallelism supported by the multicore platform. When the trusted and untrusted

threads run at the same time, the adversary still has the hardware resources to launch attacks. Therefore, the design defect becomes an exploitable vulnerability.

## 5 FULL ISOLATION ON MULTICORE PLATFORMS

In this section, we propose a new isolation paradigm to enclose an entire computing environment including the CPU core, the memory region, and (optionally) the needed peripheral device(s). Our new system is named as *fully isolated micro-computing environment* or FIMCE. It not only avoids all aforementioned security pitfalls of virtualization-based memory isolation, but also has several advantages over other memory isolation systems.

#### 5.1 FIMCE Architecture

In a nutshell, a FIMCE is an isolated computing environment dynamically set up by the hypervisor to protect a security task. The hypervisor enforces the isolation between the guest and a FIMCE by using virtualization techniques. A FIMCE consist of the minimal hardware and software satisfying the task's execution needs. Its default hardware consists of a vCPU core, a segment of main memory and a Trusted Platform Module (TPM) chip. If requested, peripheral devices (e.g., a keyboard) can be assigned to a FIMCE as well. These hardware resources are exclusively used by the task when it is running inside its FIMCE.

The code running inside a FIMCE consists of a piece of housekeeping code called the *FIMCE manager* and the software components that comprise of a set of *pillars*, as well as the security task itself. A pillar is in essence a self-contained library the security task's execution depends on. For instance, a TPM pillar provides the TPM support to the task. A FIMCE hosts a *single* thread of execution starting from the entry of the FIMCE manager. All code in a FIMCE runs in Ring 0 and calls each other via function calls. Hence, there is no context switches within a FIMCE.

**Core Isolation.** The vCPU core used by the protected task is isolated from the untrusted OS for two reasons. Firstly, it avoids the same pitfall as in the existing memory isolation primitive. Secondly, it prevents untrusted OS from interfering with the FIMCE by using the inter-core communication mechanisms such as INIT signals. In modern systems, such signals can be triggered via programming the APIC. Note that core isolation does *not* mean that a physical CPU core is permanently dedicated to a protected task. In fact, the task can migrate from one core to another. However, while it is running, it exclusively occupies the vCPU and does not share it with other threads, until it voluntarily yields the control or is terminated by the hypervisor.

In addition, the hypervisor sets up the virtual core of the isolated environment such that external interrupts, NMI, INIT signal and SIPI are all trapped to the hypervisor. By default, INIT and SIPI automatically trigger VM exit. To intercept NMI, the hypervisor sets the NMI exiting bit in the pin-based VM-Execution control bitmap of the VMCS structure. To handle external interrupts including possible IPIs, empty interrupt handlers are installed by the hypervisor inside the FIMCE, while the security task may choose to replace them with its own handlers to manage peripheral devices.

**Memory Isolation.** Memory isolation is still indispensable in FIMCE design. FIMCE guarantees that the entire address translation process is out of the guest kernel's reach. All data structures used in the translation process such as the guest page table and the Global Descriptor Table (GDT) are separated from the kernel. Moreover, the physical memory pages used by a FIMCE are allocated from a pool of pages priorly reserved by the hypervisor. Using reserved memory pages deprives the kernel of the chance to influent the mappings used inside the FIMCE. Hence the address-mapping and TLB-related issues discussed in Section 4 do not arise.

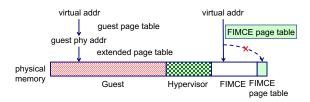

Different from conventional virtual machines, it is not necessary to turn on memory virtualization for the FIMCE. Without any EPT, the FIMCE's MMU uses the page table to translate a virtual address directly to a physical address. The main benefits of the setting are to save the hypervisor's workload of managing EPTs and to speed up FIMCE's memory access. Figure 3 explains the memory setting for a FIMCE.

Fig. 3. Memory isolation for FIMCE without EPT

When launching the FIMCE, the hypervisor sets up the page table according to the parameters that describe the virtual address space. To prevent the code in the FIMCE from accidentally or maliciously accessing pages outside of the isolated region, the hypervisor does not allow it to update the page table. In other words, the address mapping is fixed. For this purpose, the page table does not have mappings to its own physical pages and updates to the CR3 register and other control registers are trapped to the hypervisor. (Note that different paging modes make different interpretation of the same paging structure which may have loopholes allowing the FIMCE code to breach memory isolation.) Lastly, the hypervisor configures Input-Output Memory Management Unit (IOMMU) page tables to prevent illegal Direct Memory Accesses (DMAs).

I/O Device Isolation. We utilize DMA remapping and interrupt remapping supported by hardware based I/O virtualization, together with VMCS configuration and EPTs to ensure that the FIMCE has exclusive accesses to peripheral devices assigned to it. Firstly, any I/O command issued from the guest to the FIMCE device should be blocked. For port I/O devices, the hypervisor sets the corresponding bits in the guest's I/O bitmap. For Memory Mapped I/O (MMIO) devices, the hypervisor configures the guest's EPTs to intercept accesses to the MMIO region of the device.

Secondly, interrupts and data produced by a FIMCE device are only bound to the FIMCE core. For this purpose, the hypervisor configures the translation tables used by DMA and interrupt remapping. The former redirects DMA accesses from the device to the memory region inside the FIMCE and the latter ensures that interrupts from the device are delivered to the FIMCE core rather than other cores of the guest.

## 5.2 The Lifecycle of FIMCE

When the platform is powered on, its Dynamic Root of Trust for Measurement (DRTM) is invoked to load and measure the hypervisor which in turn launches the guest OS. A FIMCE is launched only when the hypervisor receives a hypercall to protect a security task. After the task completes its job, it issues another hypercall within the FIMCE to request FIMCE shutdown. We describe below the main procedures the hypervisor performs during FIMCE launch, runtime and termination.

*5.2.1 FIMCE Bootup.* The hypervisor's main tasks here are to allocate the needed hardware resources and to set up the environment for the security task.

**Hardware resource allocation.** The default FIMCE hardware resources comprise a CPU core, a set of physical memory pages, and the TPM chip. To make a graceful core ownership handover from the guest to the FIMCE, the guest OS's CPU hot-plug facility is utilized to remove a physical core

from the guest. To unplug a core, the kernel migrates all processes, kernel threads and Interrupt ReQuests (IRQs) to other cores and only leaves on the core the idle task which puts the CPU to suspension. The kernel also configures the unplugged core's local APIC so that local interrupts are masked. Note that the guest OS cannot prevent the hypervisor from gaining control of a core after a hypercall. After removal, the (benign) kernel will not attempt to use the unplugged core any longer. The hypervisor then allocates a new VMCS for the logical core of the FIMCE and initializes the VMCS control bits such that core isolation takes effect once the FIMCE starts execution.

The physical memory used by the FIMCE is allocated by the hypervisor from a reserved memory frame pool so that they are not accessible from the guest. To setup for the FIMCE's access to the TPM chip, the hypervisor blocks other cores' access to the TPM's MMIO registers by configuring the EPT.

The FIMCE may also contain peripheral devices. If the security task requires accesses to a peripheral device, the hypervisor leverages the IOMMU's capability to redirect DMA accesses and interrupts to ensure the FIMCE's exclusive ownership. The hypervisor also configures the I/O bitmap in the guest's VMCS to intercept any guest access to the device through Port I/O, and configures the EPT for accesses to the MMIO regions. The hard disk is not considered in our design because disk data can easily be protected by cryptographic means.

**Environment Initialization.** After all hardware resources are allocated, the hypervisor sets up the FIMCE environment for the task's code to run inside. Firstly, the hypervisor initializes a minimum set of data structures required by the hardware architecture. These include a Global Descriptor Table (GDT) with a code segment descriptor, a data segment descriptor and a task-state segment (TSS) descriptor. We use simple flat descriptors for both code and data segments. The descriptors are configured with a Descriptor Privilege Level (DPL) of 0, which means that all FIMCE code runs with Ring 0 privilege. There is no adverse consequence to elevate the FIMCE code's privilege, because it cannot access the guest or the hypervisor space due to full isolation. It cannot attack other FIMCE instances neither, because each FIMCE instance is independent of each other and is launched with a clean state.

An Interrupt Descriptor Table (IDT) is also initialized with entries pointing to empty interrupt handlers. With the IDT, proper interrupt handlers can be installed if the security task requests I/O support. In addition, the hypervisor sets up the page table for the FIMCE. The hypervisor also flushes the FIMCE core's TLB to invalidate all existing entries. Lastly, it properly fills in the VMCS fields to complete environment initialization.

**Code Loading.** The hypervisor first loads the FIMCE manager code into the FIMCE memory. The FIMCE manager is the hypervisor's delegate for housekeeping purposes, e.g., setting up the software infrastructure. The hypervisor then loads the security task. Based on the parameters in the FIMCE starting hypercall, the hypervisor may also load pillars. More details about the pillars and the FIMCE manager are presented in Section 7.

At the end of the boot up, the hypervisor prepares the security task's execution. If there are input parameters, it marshals them onto the FIMCE's stack and sets up the new secure stack pointer. Finally, the hypervisor passes the control to the FIMCE manager which starts execution within the isolated environment.

5.2.2 Runtime. Once the FIMCE manager takes control, the FIMCE is in the running state. It can only be interrupted by hardware events, software exceptions and non-maskable interrupts. All software exceptions and critical hardware interrupts are considered as system failure and trigger the hypervisor to terminate the FIMCE. Other interrupts are handled by the empty handlers by default

which simply return, unless their corresponding handlers are installed during FIMCE launching (as part of a pillar).

5.2.3 Termination. A FIMCE can be shutdown due to the security task's termination hypercall or due to the system failure interrupts. To turn off a FIMCE, the hypervisor zeros its memory partition and invalidates the TLBs. It then switches the current VMCS to the one used for the guest OS, re-enables the EPT on the current core. It undoes any device assignment and returns them to the OS. Lastly it notifies the OS that the core is returned back.

# 5.3 Comparisons to Memory Isolation Primitive

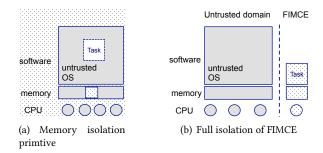

Figure 4 depicts the architectural difference between the memory isolation primitive used in existing schemes and the full isolation of FIMCE. The main distinction is the boundary between the trusted and the untrusted.

Fig. 4. The comparison between the memory isolation primitive and FIMCE. The gray regions denote resources controlled by the adversary and the dotted regions denote isolated resources.

As compared with domain isolation [16] and memory isolation, FIMCE possesses their virtues without their drawbacks. It has the well-defined isolation boundary between the trusted and the untrusted, as in domain isolation. Nonetheless it does not have a large Trusted Computing Base (TCB) as in Terra [16]. FIMCE also achieves page-level granularity as in a memory isolation scheme, e.g., TrustVisor [24]. It reuses the existing OS facility to load the security task, i.e. reading the binary from disk and constructing the virtual address space. However, once the security task is loaded, the guest OS is completely deprived of the capability to interfere with its execution. In contrast, existing memory isolation schemes allow the guest OS to do so. For example, the guest OS can extract sensitive information via page swapping, as demonstrated in [37]. Furthermore, on a multicore system, the guest OS's task scheduling makes it difficult for the hypervisor to track and enforce access control policies as shown in Section 4. The design of FIMCE also avoids the address space layout verification used in TrustVisor [24] and InkTag [18] which is vulnerable to race condition attacks.

#### 6 FIMCE AND SGX

Although virtualization-based memory isolation systems suffer from the aforementioned security pitfalls, hardware-based techniques do not. Intel SGX provides a hardware-based isolation environment for user-space programs. However, it remains as a challenging problem to use memory isolation techniques alone to protect sensitive I/O tasks, e.g., reading a password from the keyboard. Existing systems like Haven [4] rely on cryptographic techniques with a high performance toll. In the following, we compare SGX and FIMCE from various aspects and then explore potential integration.

# 6.1 Comparisons

FIMCE and SGX are designed with different goals. SGX offers the memory isolation service for applications to protect their sensitive data. Nonetheless, it still requires the OS to manage platform resources, including the enclaves and the associated Enclave Page Cache (EPC) pages. FIMCE is geared to isolate a complete computing environment and therefore covers all hardware and software resources needed by the protected task. The wider coverage allows FIMCE to offer unique advantages over SGX in several aspects.

Memory Isolation. SGX and FIMCE provide different strengths of memory isolation. SGX's isolation is tightly integrated with hardware. The TCB only consists of the underlying hardware which is the SGX enabled CPU and the firmware. The system software is considered as untrusted in SGX's model. The EPC-related memory access check is performed after address translation and before physical memory access [11]. When the processor is not in enclave mode, no system software, including the System Management Mode (SMM) code, can access the content inside an enclave. Data is also encrypted by the hardware when it is written to EPC pages. It is hence secure against bus snooping attacks. FIMCE isolation leverages hardware-assisted virtualization techniques. Besides the underlying hardware and firmware, the TCB of FIMCE also encloses the micro-hypervisor which has several thousands SLOC. No encryption is applied when the isolated code writes to the FIMCE memory. Therefore, FIMCE is strictly weaker than SGX in terms of blocking illicit memory accesses.

When the code inside the SGX enclave accesses non-EPC pages, SGX provides *no* security assurance at all. The malicious OS may proactively present a faked memory view to the enclave by using manipulated page tables. In contrast, the code inside the FIMCE accesses all memory pages without obstruction from the OS as the paging structures in use are entirely beyond the OS's control. FIMCE has stronger security from this perspective.

**Autonomous Execution.** SGX and FIMCE give different treatments of CPU scheduling of the isolated program. SGX leaves thread scheduling inside the enclave to the OS. This design decision allows for the page fault attack [37] wherein the guest OS interrupts the enclave execution and exfiltrates sensitive data.

FIMCE isolates a physical core and exposes a smaller attack surface to the OS. The guest OS cannot influence the execution of the FIMCE thread. Page faults inside the FIMCE are handled internally. It is hence a highly autonomous system with no runtime dependency on the OS.

I/O Capability. SGX does not support I/O operations. Secure data exchange between an enclave and the outside world becomes a challenging task. As shown by Haven [4] and SCONE [1], a middle layer between the isolated application and the OS is introduced to ensure data confidentiality and authenticity via cryptographic means. This approach entails significant performance overhead, due to the costly context switches to/from the enclave as well as the cryptographic operations. According to SCONE [1], the I/O intensive benchmarks such as Apache and Redis suffer 21% and 31% performance loss, respectively. Similar results are also reported in Haven.

FIMCE provides inherent I/O support for the isolated tasks. I/O device isolation guarantees exclusive accesses to peripheral devices. Although whitelisted device drivers are still needed, the OS layer abstraction such as sockets or filesystems could be simplified. Furthermore, since the device is isolated and accessed in an exclusive manner, cryptographic protection is no longer needed. Note that context switch costs are also saved as no context switch is required inside the FIMCE.

**Verifiable Launch.** SGX and FIMCE also differ in controlling the launch of the isolated environment. Although SGX supports attestation, it does not enforce policies for enclave launch. The permission to launch an enclave is decided by the untrusted OS. In FIMCE's design, the trusted

hypervisor can verify the environment to be launched against the security policies (if any). For instance, the platform administrator may supply a signed whitelist to the hypervisor to specify permissible tasks.

## 6.2 Integration with SGX

SGX and FIMCE are not mutually exclusive to each other. It is possible to integrate both so that one's strength complements the other's weakness. In the following, we discuss possible ways to combine them.

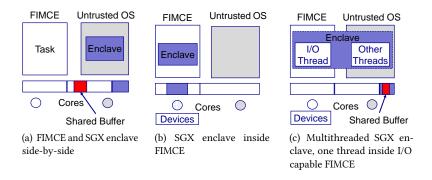

Fig. 5. FIMCE based isolated I/O for SGX enclaves

**Share Memory Between Enclave and FIMCE.** A naive integration is to run the SGX enclave and the FIMCE side-by-side (as in Figure 5(a)) with a shared memory buffer used for intercommunication. Unfortunately, it is hard to secure FIMCE-enclave data exchange in this fashion.

We observe that the shared buffer has to be on a non-EPC page. Otherwise, the task isolated by the FIMCE cannot access it even with the hypervisor's assistance. Since the shared buffer is outside of the enclave, SGX provides no assurance on the security of accessing them. Although the hypervisor is trusted under the FIMCE model, protecting the shared buffer using virtualization faces the same issues elaborated in Section 4. Hence, it is not a promising approach to integrate SGX and FIMCE as two separated environments in parallel.

**Enclave Inside FIMCE.** Since loading a FIMCE within an enclave is infeasible, the next plausible approach is to launch an enclave inside a FIMCE (as in Figure 5(b)). The security benefits of the combination are twofold. As compared to SGX isolation alone, the adversary has no more control over the FIMCE/enclave core. Hence, the composite isolation eliminates those SGX side-channel attacks that require interleaved executions on the core. As compared to FIMCE isolation, the composite isolation is not subject to bus snooping attacks by virtue of SGX protection.

To support SGX enclaves inside the FIMCE, the hypervisor priorly reserves a pool of EPC pages for FIMCE usage. This can be achieved by using normal EPT mappings during boot up, as already implemented in KVM <sup>2</sup>. Running with Ring 0 privilege, the FIMCE manager takes up the kernel's responsibility to set up and manage the enclave.

Specifically, the FIMCE environment is created and launched as described before, except that the protected task and pillars are loaded with Ring 3 privilege. To create the enclave, the FIMCE manager executes SGX special instructions such as EINIT. It then assigns EPC pages from the reserved pool to the enclave, and issues EADD to add those needed FIMCE pages. After setting up

<sup>&</sup>lt;sup>2</sup>KVM patch note at https://www.spinics.net/lists/kvm/msg149534.html

the enclave, the manager passes the control to the protected task which then issues EENTER to enter into the enclave.

**Multithreaded I/O.** A direct benefit of the design in Figure 5(b) is that the code in the enclave can securely interact with I/O devices via the FIMCE environment. The design can be further extended to support multithreaded I/O operations as depicted in Figure 5(c).

The idea is to leverage SGX multithread support. The main thread protected by SGX spawns one special thread dedicated for I/O operations. After the enclave is created, the hypervisor migrates the I/O thread into the FIMCE following the design in Figure 5(b). The FIMCE manager runs the EENTER instruction with the supplied Thread Control Structure (TCS) that uniquely identifies the I/O thread. Hence, the thread running on the FIMCE core and the main thread on the original SGX core belong to the same enclave. The threads intercommunicate through a shared buffer on the allocated EPC pages. The hardware ensures that only those threads belong to the same enclave can access the buffer.

When the main thread needs to access the device, it places a request in the shared buffer. The request is served by the I/O thread inside the FIMCE whereby the FIMCE's device pillars which then perform the desired I/O operations. Similarly, incoming I/O data can be securely forwarded back to the main thread.

The OS may create a fake FIMCE environment when the I/O thread's enclave is created. To detect the attack, the main thread inside the enclave can request the I/O thread to perform an attestation about the underlying environment. Note that after the I/O thread is migrated into the FIMCE, it is no longer under the OS scheduling.

## 7 MODULARIZED SOFTWARE INFRASTRUCTURE

It is widely recognized that existing memory isolation schemes require the protected task to be self-contained. In contrast, FIMCE has the inborn support for dynamically setting up the software infrastructure e.g., libraries, drivers and interrupt handlers, to cater to the task's needs. We propose to use a structured way to construct the FIMCE software infrastructure. Based on their functionalities, a set of software modules called *pillars* are stored in the disk in the form of Executable and Linkable Format (ELF) files. A pillar is a self-contained shared library for a particular purpose. For instance, a TPM pillar consists of all functions needed to operate the TPM chip. Based on the protected task's demand, the guest OS loads the needed pillar files from the disk to the memory. Then, the hypervisor relocates them into the FIMCE after integrity checking. The main challenges here are how to ensure the integrity of pillar and how to check correctness of linking without significantly increasing the hypervisor's code size.

## 7.1 Pillars

Pillars provide services that are otherwise not easily available to the security task due to the absence of OS in the FIMCE. Each pillar is assigned with a globally unique 32-bit *pillar identifier* (PLID). Each function that a pillar exports is assigned with a locally unique 32-bit *interface identifier* (IID). Therefore, a (PLID, IID) pair uniquely identify a function in the whole system.

Pillars resemble legacy shared libraries to a large extent. They are compiled as position-independent code because the actual position of a pillar in memory is not determined until it is loaded. They reside in disks as files in the ELF format (for Linux). A pillar differs from a shared library in two aspects. Firstly, a pillar must be self-contained. The code of a pillar function does not depend on any code outside of the pillar. Secondly, the ELF format of a pillar has a new section called pillar descriptor (.p\_desc) which contains the pillar's PLID, the description of exposed interfaces, and a signature from a Trusted Third Party (TTP).

**Pillar Loading.** To reduce the hypervisor's workload, the application hosting the security task requests the guest kernel to load the needed pillars into the guest memory as regular shared libraries. When the application issues a hypercall to request FIMCE protection for its security task, the parameters passed to the hypervisor include the needed pillars' PLIDs and their memory layouts. Given the PLID, the hypervisor locates the corresponding pillar in the guest memory, copies it into the FIMCE memory and maps the pillar pages at the same virtual addresses as in the guest. By relying on the guest to manage the pillars in the memory, the hypervisor does not need to support filesystems or disk operations.

# 7.2 Pillar Verification and Linking

Once the needed pillars and the security task are loaded into the FIMCE, the hypervisor passes the control of the core to the FIMCE manager code. If the manager code verifies pillar integrity successfully, it links the security task to the pillars and passes the control to the entry point of the security task.

7.2.1 Pillar verification. Integrity verification is not as straightforward as it seems because it is infeasible to verify the pillar as one whole chunk. The shared library loading procedure may zero some sections and the kernel also performs dynamic linking and running of the library initialization code as well. These operations result in discrepancies between the pillar's memory image and its file in the disk.

Nonetheless, shared libraries are compiled into position independent code that is expected to remain unaltered throughout the loading process. Therefore, the authentication tag of a pillar is a TTP signature protecting the following invariant sections: code sections, data sections, library initialization sections, finish sections, the pillar descriptor section and the section header table of the pillar ELF file. If the verification fails, the manager issues a hypercall to terminate the FIMCE and an error is returned to the application.

Global symbol references within a pillar are also subject to attacks by the guest kernel. Such references are completed with the assistance of the Procedure Linkage Table (PLT) and the Global Offset Table (GOT) inside the module itself. The entries are typically filled by the loader in the guest. In order to thwart possible attacks, the dynamic symbol table, relocation entries and the string table of the pillar are also signed by the TTP. During loading time, the dynamic loader are explicitly requested to resolve all symbols, so that all GOT entries are filled. After the pillar is loaded into the FIMCE, these values are then verified by the FIMCE manager against the corresponding relocation entry to ensure that they refer to the correct locations.

7.2.2 Dynamic Linking. Although the kernel has the capability of linking pillars with the security task, we can hardly benefit from the kernel's assistance because of potential attacks. A function call to another object file is normally compiled to a call to an entry in the PLT in the originating object file. Because the hypervisor lacks sufficient semantics to determine which entries in the PLT are genuine ones used by the security task, it is costly for the hypervisor to bridge the gap.

We devise a novel lightweight scheme to link the security task with pillar functions at runtime within the FIMCE. The idea is to introduce a *resolver* function and a *jump table* as part of the FIMCE manager. Both are placed at fixed locations in the FIMCE address space by the hypervisor during FIMCE setup. After verifying all pillars loaded in the FIMCE, the manager parses their descriptor sections and fills the jump table with entries corresponding to each available interface. A jump table is in essence a sorted array of (PLID, IID, entry-address).

A function call from the security task to a pillar function is replaced by a call via a function pointer which takes the original input parameters as well as a pair of (PLID,IID) with a parameter counter. At runtime, the function pointer is assigned with the resolver function's address. After

being called, the resolver rearranges the stack according to the parameter counter, looks up the jump table to find the entry address of the callee function, restores the stack frame used before the call and uses an unconditional jump to redirect execution to the entry. The callee function executes as if it were called directly by the security task, and returns to the security task after execution.

## **8 APPLICATIONS OF FIMCE**

Besides isolation, FIMCE can be applied to other types of applications. In the following, we discuss two new types of applications. The first application taps into FIMCE malleability to protect a program's long term secret. The second one establishes a runtime trust anchor by exploring the parallelism between a FIMCE and the guest kernel.

# 8.1 Malleability

The FIMCE environment can be configured in a non-standard fashion because its hardware setting is prepared by the hypervisor for the isolated task's exclusively use. For instance, the hypervisor can twist the CPU registers and even the TPM configuration.

To demonstrate the benefit of malleability, we consider the challenge of ensuring that an application P's long term secret k can only be accessed in its isolated environment. Suppose that k has been initially encrypted with the binding to the isolated environment. The difficulty lies in how to authenticate the thread that requests to enter into the isolated environment. Note TPM's sealed storage *alone* cannot directly solve this problem. Sealed storage is a mechanism to bind a secret to a set of Platform Configuration Registers (PCRs) on the TPM chip. Since most PCRs can be extended by software, the PCR values are dependent on the software that extends them. Therefore, without a proper access control on the PCRs, PCR values do not truly reflect the environment states. Under our adversary model, the default locality-based access control is not adequate.

Since the application cannot hide any secret in the unprotected memory against the OS, both have the equal knowledge and capability in terms of presenting the authentication information to the hardware. One may suggest to leverage the hypervisor to perform authentication as shown in [24]. However, as we have analyzed in Section 4.3, it is challenging for the hypervisor to securely authenticate the application without sufficient knowledge about the kernel level semantics.

With a malleable environment, FIMCE offers an elegant solution. The hypervisor uses the TPM Locality 2 and assigns the OS with Locality 0 and the code inside a FIMCE with Locality 1. During boot up, the DRTM extends PCR17 and PCR18 with the hypervisor and other loaded modules. When a FIMCE is launched, the hypervisor resets PCR20 and extends PCR20 with all code and data loaded in the FIMCE. The protected code in turn extends it with all relevant data, and seals the secret k with PCR17, PCR18 and PCR20. Once the seal operation is done, it extends PCR20 with an arbitrary binary string to obliterate PCR20 content and relinquishes its Locality-1 access so that the OS is free to use the TPM. The same steps are performed in order to unseal k.

Note that PCR17 and PCR18 are in Locality 4 and 3 respectively. The hardware ensures that they cannot be reset by any software. During the boot up, the DRTM extends these two registers with the loaded modules. Their correct content implies the loading time integrity of the hypervisor. Since the OS is in Locality 0, it does not have the privilege to extend or reset PCR20, even though it can prepare the same input used by the hypervisor and application P. Other (malicious) applications in their own FIMCEs cannot impersonate P either. PCR20 stores the birthmark of a FIMCE instance because the code in a FIMCE cannot reset PCR20. Therefore, other applications cannot remove their own birthmarks to produce the same digest as P does.

The advantage of our method is that the hypervisor does not hold any secret and is oblivious to the application's logic and semantics. Besides the stronger security bolstered by the hardware, it has a small TCB and supports process migration.

#### 8.2 Runtime Trust Anchor

Another noticeable strength of FIMCE is its ability to provide an isolated environment that securely runs in parallel with the untrusted OS yet without suffering from the semantic gap. The environment can host a trust anchor to tackle runtime security issues such as monitoring and policy enforcement. To show the benefit of a runtime trust anchor, we sketch out two systems below.

The first system is to prevent sensitive disk files from being modified or deleted by the untrusted OS. This problem has been studied by Lockdown [36] and Guardian [7]. Lockdown suffers from performance loss as every disk I/O operation entails a VM exit (if not optimized) while the approach used in Guardian cannot be applied for arbitrary files chosen by applications. In our approach, a FIMCE is used as the disk I/O checkpoint. the hypervisor isolates the disk to the FIMCE. A disk I/O filter is loaded in the FIMCE. It continuously reads from a share buffer the disk-related Direct Memory Access (DMA) requests placed by the OS. If the request is compliant with the security policy, the filter forwards it to the disk controller. Otherwise, it drops the request. All disk interrupts are channeled to the OS so that the filter is not necessarily involved in handling them. In this design, the filter is isolated from the guest and the DMA requests are always checked without the cost for VM exit and entry.

The second system is about the runtime attestation of the OS behavior. Most existing remote attestation schemes [21, 24, 27] focus on loading time integrity check. It is challenging to realize runtime attestation because it requires the attestation agent to run securely inside the attesting platform managed by an untrusted OS. With FIMCE protection, the agent runs like an isolated kernel thread side-by-side with the OS. The attestation agent can read the kernel objects without facing the challenging semantic gap problem [14, 15, 19, 30]. To support kernel memory read, the entire kernel page table is copied into the FIMCE. The hypervisor properly configures the EPTs such that only the agent code pages are executable in order to prevent untrusted kernel code from executing inside the FIMCE.

We observe that it is difficult, if not impossible, to solve the attestation problem using the existing memory isolation primitive. If the untrusted guest OS still manages the CPU cores, it can schedule off the attestation agent from the CPU before its attacks and resumes it afterwards. Hence, the attestation does not reflect the genuine state of the kernel.

#### 9 EVALUATION

In this section, we first discuss the security of FIMCE by a comparison with memory isolation. We then report our prototype implementation as well as the benchmarking and experimental results.

# 9.1 Security Analysis

It remains as an open problem to formally prove the security of a system design (not implementation). Therefore, the security analysis below is informal. We first argue that the multicore complications plaguing memory isolation systems are not applicable to our design. We then evaluate FIMCE security based on its attack surface and TCB size.

**Complication Free.** Recall that Section 4.3 has enumerated three security complications due to the multicore setting, namely complex EPT management, insecure guest page table checking and incapable thread identification. Since the FIMCE is a fully isolated environment, its design does not face these three complications.

• The EPT management of FIMCE is rather simple. The EPTs used for the OS (and the applications) are not affected by FIMCE. Since the trusted and untrusted execution flows do not interleave with each other on any CPU core, the hypervisor does not need to trace the executions in order to switch EPTs. In addition, the attacks in Section 3 that exploit stale

TLB entries are infeasible. The physical memory of the FIMCE is never accessed by threads outside of the environment. Moreover, when a FIMCE is terminated, the TLB entries in the core are all flushed out. Hence, there is no stale TLB entry in the system.

- FIMCE does not suffer from the issue of guest page table checking. The execution inside the FIMCE has no dependence on data controlled by the guest OS including the page tables, which makes Iago-like attacks impossible. It is also clear that the full isolation is not subject to the race condition attack described in Section 4.3.

- Memory isolation schemes need subject identification to choose the proper EPT setting. This challenging problem does not exist in our scheme. The isolated task is bound to the FIMCE created for it through its whole lifetime. It exclusively accesses the memory. The task may continue the execution without being preempted by other threads under the OS's control. In case that it relinquishes the CPU, its FIMCE hibernates without changing ownership. In other words, all memory states and the CPU context are saved. The CPU states are cleaned up before the OS takes control. When needed, the FIMCE is re-activated from the saved state. Therefore, subject identification is not needed.

**Reduced Attack Surface.** The malicious kernel in memory isolation systems enjoys a large attack surface, as it has the full control over the CPU cores and the VA-to-GPA mapping, which leads to various attacks and design complications described in Section 3 and 4. In contrast, the attack surface exposed by FIMCE is reduced.

Owing to the full isolation approach, the FIMCE's hardware and software are beyond the kernel's access, interference and manipulation. The kernel cannot access the FIMCE core's registers, L1 and L2 caches. L3 cache is not effectively accessible either because the FIMCE's host physical address region is never mapped to the guest. Although the kernel may use IPI or NMI to interrupt the FIMCE, the worst consequence is equivalent to a DoS attack. Since the isolated code handles the interrupts by itself, an IPI or NMI only results in a detour of the control flow. Note that there is no context switch inside the FIMCE.

Another attack vector widely considered in the literature is the interaction between the hypervisor and the kernel. The FIMCE hypervisor only exports two hypercalls, for setting up and terminating the FIMCE respectively. Moreover, the hypervisor does not interpose on either the guest execution or the FIMCE execution.

The FIMCE may exchange data with threads in the outside environment. In that case, the malicious kernel may poison the input data to the isolated task. We acknowledge that the protected code is subject to such attacks if no proper input checking is in place. However, it is out of scope of our work to sanitize the inputs.

**Strength of Full Isolation.** The FIMCE isolation is enforced by the hardware. The memory used by the FIMCE is from a reserved physical memory region which is never mapped to the guest by the EPT and the IOMMU page table. Both segmentation and paging of the FIMCE memory are constructed by the hypervisor. It is thus obvious that the attacks in Section 3 do not work against the FIMCE. The guest kernel cannot make modifications to either segmentation- or paging-related data structures to tamper with the address space.

**Security of Foreign Code in FIMCE**. In addition to the security task, the FIMCE hosts the needed pillars and the FIMCE manager. It is crucial to ensure the integrity of their code and the linking process. The FIMCE manager's code is *copied* from the hypervisor space. Therefore, its integrity is ensured as long as the hypervisor is trusted.

During FIMCE launching, the integrity of the loaded pillars' code images (including the relocation sections) are verified by the FIMCE manager in order to prevent the kernel from poisoning them. To

ensure linking integrity, the jump table is constructed using the verified pillar description sections. Addresses in the GOT entries used for symbol references within a pillar are also checked by the FIMCE manager to match the corresponding addresses computed from the pillar's relocation-related sections.

**Small TCB Size.** The hypervisor is the *only* trusted code in the system. With a simple logic, our hypervisor has a tiny code base with around six thousand lines of source code for runtime execution. It is easy to manage concurrency in the hypervisor space. Because only the setup and teardown code possibly execute concurrently on different cores, they can be synchronized with simple spinlocks. Note that each FIMCE instance does not have overlapping regions, which also help simplify concurrency handling.

# 9.2 Implementation

We have implemented a prototype of FIMCE on a desktop computer with an Intel Core i7 2600 quad-core processor running at 3.4 GHz, Q67 chipset, 4GB of DDR3 RAM and a TPM chip. The platform runs a Ubuntu 12.04 guest with the stock kernel version 3.2.0-84-generic. We have implemented the FIMCE hypervisor of around 6000 source line of code (SLOC). It exports two hypercalls, i.e., FIMCE\_start() and FIMCE\_term(), for starting and terminating a FIMCE, respectively. The TCB of FIMCE only consists of the TXT bootloader, the hypervisor and any hardware and firmware required by DRTM. We slightly modify Intel's open source TXT bootloader *tboot*<sup>3</sup> to load our hypervisor. The modification is to make the bootloader jump to the FIMCE hypervisor's entry at the end of the boot up sequence. During hypervisor initialization, a set of EPT entries are initialized such that a chunk of physical memory is reserved for exclusive use by the hypervisor. During the OS kernel initialization, all cores are set to use the same set of EPTs, ensuring a uniform view of the memory.

To showcase the applications of FIMCE, we have also developed three pillars: a 7KB serial port driver pillar that supports keyboard I/O, a comprehensive crypto pillar of 451KB size based on the mbed TLS library  $^4$ , a TPM driver pillar of 20KB size. The implementation also encloses a FIMCE management code of 413 SLOC which verifies and links pillars in use.

**Programming Interface** As shown in Table 1, the user space FIMCE library provides two interfaces and three macros. The two interface functions are used to start and stop the FIMCE, respectively. They are in essence wrappers of the hypercalls to pass parameters to the hypervisor. The first two macros are for the application developer to specify the function to be protected, as well as the ELF file names of pillars to be loaded. The third macro converts a normal C function call into a pillar function call. (Note that the dynamic linking mechanism in a FIMCE is different from in the OS.)

| Interface              | Description                                |

|------------------------|--------------------------------------------|

| start_FIMCE ()         | Call to start FIMCE                        |

| stop_FIMCE ()          | Call to stop FIMCE                         |

| Macros                 |                                            |

| FIMCE_SECURITY_TASK () | Specify function that is the security task |

| FIMCE_LOAD_PILLAR ()   | Specify the file name of the pillar        |

| CALL PIL ()            | Call a pillar function in a security task  |

Table 1. User Space Library Interfaces and Macros

**Internals of start\_FIMCE()** This user space function runs in two steps in the guest domain. Firstly, it helps to load all data and code needed by the hypervisor into the main memory. It finds

<sup>&</sup>lt;sup>3</sup>http://sourceforge.net/projects/tboot/

<sup>4</sup>https://tls.mbed.org/

the address of FIMCE\_PAYLOAD from the symbol table and the locations of needed pillars, including the base addresses and lengths of all segments with assistance of the dynamic loader. To ensure that the contents are indeed loaded into memory, it reads all pages of the pillars.